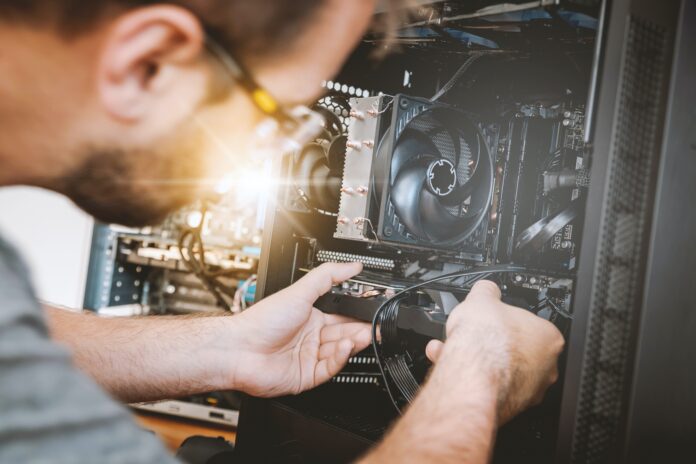

Cache is a critical component of modern computer systems that plays a crucial role in improving performance by reducing the time it takes to access frequently used data. It serves as a high-speed memory that resides between the processor and the main memory, storing copies of recently accessed data or instructions. By keeping frequently accessed information closer to the processor, cache minimizes the latency associated with accessing data from the main memory, which is significantly slower in comparison. In this article, we will delve into the details of cache, its functions, and its importance in computer systems.

Cache operates on the principle of locality, which refers to the tendency of a program to access data and instructions that are close to each other in time or space. This principle forms the basis for cache’s effectiveness. When the processor requests data from memory, the cache checks if the data is already present in its storage. If the data is found in the cache (known as a cache hit), it can be accessed quickly, saving valuable time. However, if the data is not present in the cache (known as a cache miss), the processor needs to retrieve it from the slower main memory, incurring a higher latency. To optimize performance, cache is designed to exploit the locality of data access and minimize cache misses.

Here are ten important things you need to know about cache:

1. Cache Hierarchy: Modern computer systems employ a multi-level cache hierarchy, consisting of multiple levels of cache with varying sizes and speeds. The hierarchy typically includes a small and fast Level 1 (L1) cache, a larger Level 2 (L2) cache, and sometimes even a Level 3 (L3) cache. Each level of the cache hierarchy offers progressively larger capacity but with increased latency.

2. Cache Coherency: In multi-core or multi-processor systems, cache coherency ensures that all caches in the system have a consistent view of memory. It prevents data inconsistencies that could arise from multiple cores or processors accessing and modifying the same memory location simultaneously.

3. Cache Replacement Policies: When the cache is full and a new piece of data needs to be stored, cache replacement policies determine which data to evict from the cache. Common replacement policies include the Least Recently Used (LRU), where the least recently accessed data is evicted, and Random, where data is selected randomly for eviction.

4. Write Policies: Cache write policies define how write operations are handled. Two common policies are write-through and write-back. In write-through, data is written to both the cache and the main memory simultaneously, ensuring consistency but potentially increasing memory traffic. In write-back, data is initially written only to the cache, and the main memory is updated later, reducing memory traffic but requiring additional bookkeeping.

5. Cache Associativity: Cache associativity determines how cache entries are mapped to physical locations in the cache. Direct-mapped caches allow each cache entry to be mapped to a specific location, while fully associative caches permit any entry to reside in any location. Set-associative caches strike a balance between the two, where each entry can reside in a subset (set) of cache locations.

6. Cache Line Size: The cache line, also known as cache block or cache segment, represents the unit of data that is transferred between the cache and the main memory. Larger cache line sizes increase the spatial locality by fetching more data in a single access, but may also lead to increased cache pollution if the accessed data is smaller than the line size.

7. Instruction Cache and Data Cache: Cache is often divided into separate instruction and data caches. The instruction cache stores instructions fetched from memory, while the data cache holds data accessed by the processor. This separation allows simultaneous instruction fetching and data access, improving overall performance.

8. Cache Pre-fetching: To further reduce cache misses, cache pre-fetching techniques are employed. These techniques predict and fetch data or instructions that are likely to be accessed in the near future, based on past patterns or program behavior. Pre-fetching can hide memory latency by bringing data into the cache proactively.

9. Cache Synchronization: In multi-threaded systems, cache synchronization mechanisms like cache coherence protocols and memory barriers are used to ensure proper ordering and consistency of memory operations across different threads or processors.

10. Cache Size and Performance Trade-offs: Cache size directly impacts performance and cost. Larger caches can store more data and reduce cache misses, improving performance. However, larger caches are more expensive to manufacture and can introduce higher latency. Designers must strike a balance between cache size, performance, and cost to optimize the overall system design.

Cache is a critical component of modern computer systems that plays a crucial role in improving performance by reducing the time it takes to access frequently used data. It serves as a high-speed memory that resides between the processor and the main memory, storing copies of recently accessed data or instructions. By keeping frequently accessed information closer to the processor, cache minimizes the latency associated with accessing data from the main memory, which is significantly slower in comparison.

Cache operates on the principle of locality, which refers to the tendency of a program to access data and instructions that are close to each other in time or space. This principle forms the basis for cache’s effectiveness. When the processor requests data from memory, the cache checks if the data is already present in its storage. If the data is found in the cache (known as a cache hit), it can be accessed quickly, saving valuable time. However, if the data is not present in the cache (known as a cache miss), the processor needs to retrieve it from the slower main memory, incurring a higher latency. To optimize performance, cache is designed to exploit the locality of data access and minimize cache misses.

Modern computer systems employ a multi-level cache hierarchy, consisting of multiple levels of cache with varying sizes and speeds. The hierarchy typically includes a small and fast Level 1 (L1) cache, a larger Level 2 (L2) cache, and sometimes even a Level 3 (L3) cache. Each level of the cache hierarchy offers progressively larger capacity but with increased latency.

In multi-core or multi-processor systems, cache coherency ensures that all caches in the system have a consistent view of memory. It prevents data inconsistencies that could arise from multiple cores or processors accessing and modifying the same memory location simultaneously.

Cache replacement policies determine which data to evict from the cache when it is full and a new piece of data needs to be stored. Common replacement policies include the Least Recently Used (LRU), where the least recently accessed data is evicted, and Random, where data is selected randomly for eviction.

Cache write policies define how write operations are handled. Two common policies are write-through and write-back. In write-through, data is written to both the cache and the main memory simultaneously, ensuring consistency but potentially increasing memory traffic. In write-back, data is initially written only to the cache, and the main memory is updated later, reducing memory traffic but requiring additional bookkeeping.

Cache associativity determines how cache entries are mapped to physical locations in the cache. Direct-mapped caches allow each cache entry to be mapped to a specific location, while fully associative caches permit any entry to reside in any location. Set-associative caches strike a balance between the two, where each entry can reside in a subset (set) of cache locations.

The cache line, also known as cache block or cache segment, represents the unit of data that is transferred between the cache and the main memory. Larger cache line sizes increase the spatial locality by fetching more data in a single access, but may also lead to increased cache pollution if the accessed data is smaller than the line size.

Cache is often divided into separate instruction and data caches. The instruction cache stores instructions fetched from memory, while the data cache holds data accessed by the processor. This separation allows simultaneous instruction fetching and data access, improving overall performance.

To further reduce cache misses, cache pre-fetching techniques are employed. These techniques predict and fetch data or instructions that are likely to be accessed in the near future, based on past patterns or program behavior. Pre-fetching can hide memory latency by bringing data into the cache proactively.

In multi-threaded systems, cache synchronization mechanisms like cache coherence protocols and memory barriers are used to ensure proper ordering and consistency of memory operations across different threads or processors.

Cache size directly impacts performance and cost. Larger caches can store more data and reduce cache misses, improving performance. However, larger caches are more expensive to manufacture and can introduce higher latency. Designers must strike a balance between cache size, performance, and cost to optimize the overall system design.

In conclusion, cache plays a vital role in modern computer systems by reducing memory latency and improving overall performance. Its multi-level hierarchy, replacement policies, associativity, write policies, and synchronization mechanisms contribute to its effectiveness. Understanding the principles and characteristics of cache is crucial for designing efficient computer architectures and optimizing software performance.